|        | Model Parameters | Model         |

|--------|------------------|---------------|

| CEIUPM | 2011             | 3 POLITÉCNICA |

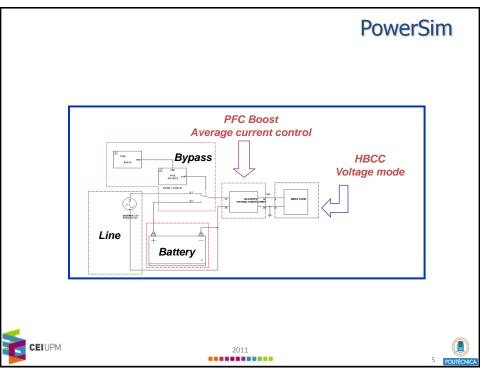

INNOVA "Power distribution and management of High Voltage loads"

CENIT DEIMOS "Development and Innovation on Polimer Membrane and Solid Oxid Fuel Cells

- •More Electric Aircraft Arquitectures modeling and simulation

- •High Voltage Distribution Network (270V<sub>DC</sub>)

- •Intelligent load management

- Auxiliary Power Units based on Fuel Cells

2011

# BATTERY MODELING FINANCIAL STATES OF THE PROPERTY OF THE PROP

# **Motivation**

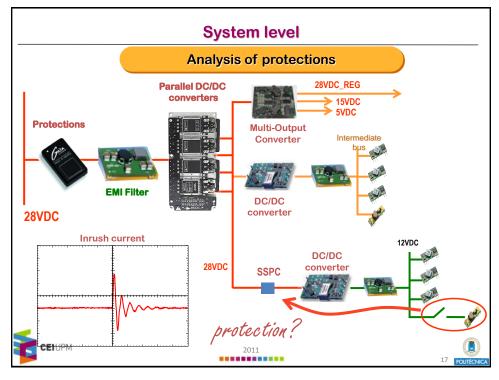

- Every electric circuit requires protection against shortcircuits and overloads.

- The rest of components need to be protected and isolated from the source of failure.

- There are many kinds of switches available:

Fuses Circuit Breakers SSPCs

2011

POLITÉCNIC

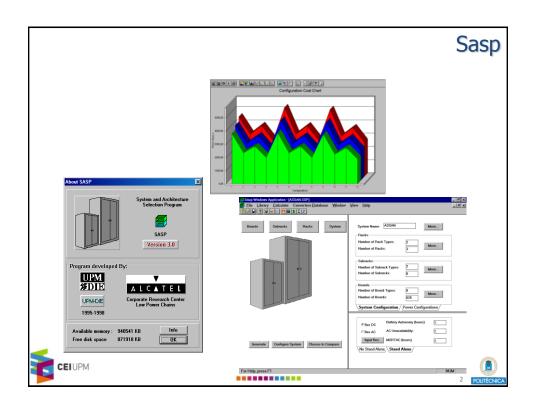

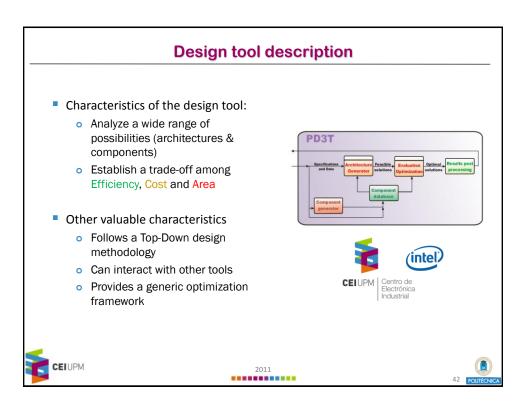

# Power Distribution Architectures Design Tool

cei@upm.es

Leonardo Laguna Ruiz

Universidad Politécnica de Madrid

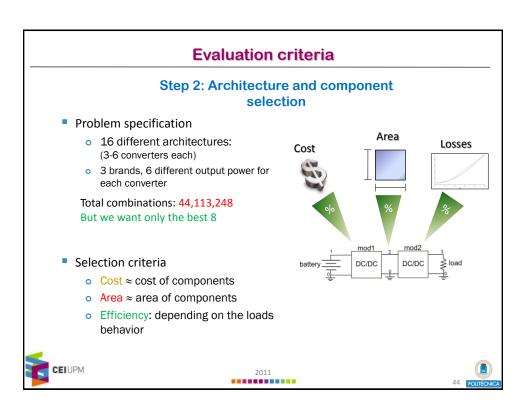

# **Example application** Input: Feed 3 loads from a source using 100 converters from a database: Source → 12 V load3 load2 load1 area and cost models • Load1 $\rightarrow$ 1.1 V Problem definition Converter database Load2 → 3.3 V Load3 → 5.0 V **Step 1: Architecture Generator** Output: (Some) Possible architectures 2011

# **Optimization (search) of best solutions** • How to find the best 8 among 44,113,248 solutions? Evolutionary algorithms · Harmony search Searching the best solutions with Harmony Search · Genetic algorithms Título · Tabu search 2000 Using Harmony Search less than 1500 0.05% of solution space is explored - Objective function of the 8th solution to find the optimal solution - Objective function of the 1th solution CEIUPM 2011 ......

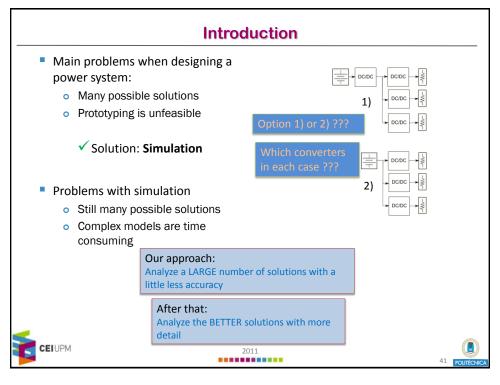

# Introduction

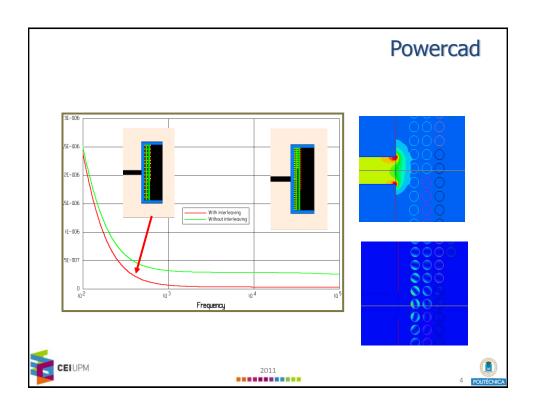

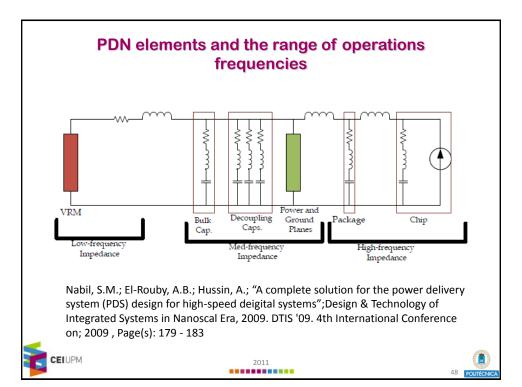

The power supply cannot be connected directly to the Vdd and Gnd terminals of the IC. It is necessary to use wires, these wires creates both a DC drop and time-varying fluctuation of the voltage. The voltage fluctuation can cause the following problems:

- Reduction in voltage across the power supply terminals of the IC that slows down the transistor or prevents the transistor from switching states.

- Increase in voltage across the power supply terminals of the IC, which creates reliability problems.

- Timing margin errors caused by degraded waveforms at the output of the drivers.

2011

OLITÉCNIC

## **VRM**

- Provides the power to the chip.

- The main influence is in low frequency (below of megahertz range).

L. D. Smith, R. E. Anderson, D. W. Forehand, T. J. Pelc, and T. Roy, "Power distribution system design methodology and capacitor selection for modern CMOS technology," IEEE Transactions on Advanced Packaging, vol. 22, no. 3, pp. 284-291, Aug. 1999.

2011

...........

# **Decoupling capacitors**

The capacitors are surface mount devices (SMDs) attached to pads on the PCB or package. When SMD capacitors supply charge (or current), the current leaves the voltage plane, travels through the voltage via, flows through the capacitor, and returns through the ground via and then to the ground plane. These contributes to increase the ESL.

L. D. Smith, R. E. Anderson, D. W. Forehand, T. J. Pelc, and T. Roy, "Power distribution system design methodology and capacitor selection for modern CMOS technology," IEEE Transactions on Advanced Packaging, vol. 22, no. 3, pp. 284-291, Aug. 1999

...........

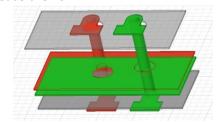

# Modeling the planes

Planes play a very important role at high frequencies by acting as high-frequency capacitors, serving as conduit for the transportation of current, and supporting the return currents of the signal lines referenced to it. Planes are large metal structures separated by a thin dielectric and are invariably used in all high-frequency packages and boards for power delivery and shielding.

Madhavan Swaminathan; A. Ege Engin, *Power Integrity Modeling and Design for Semiconductors and Systems*, Prentice Hall, 2007.

CEIUPM

2011

# Vias and chip characteristics

Each new technology generation results in a rapid increase in circuit densities and interconnect resistance, faster device switching speeds, and lower operating voltages. These trends lead to microprocessor designs with increased current densities and transition rates and reduced noise margins. The large currents and interconnect resistance cause large, resistiveIR voltage drops, while the fast transition rates cause large inductive LdI/dt voltage drops in on-chip power distribution networks.

M. Swaminathan, J. Kim, I. Novak, and J. P. Libous, "Power distribution networks for system on package: status and challenges," *IEEE Transactions on Advanced Packaging*, vol. 27, no. 2, pp. 286-300, May 2004

----

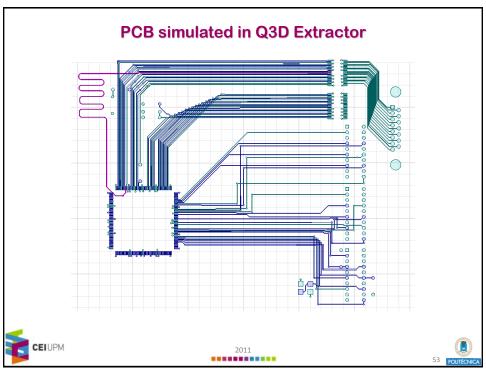

52

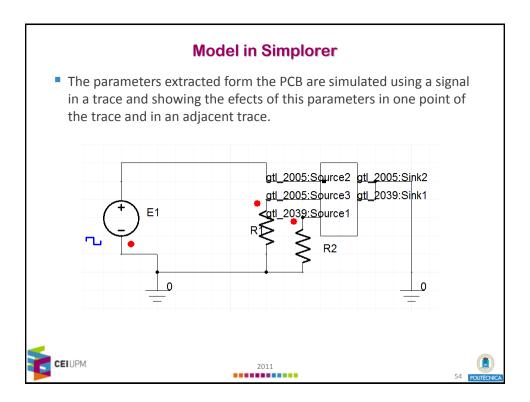

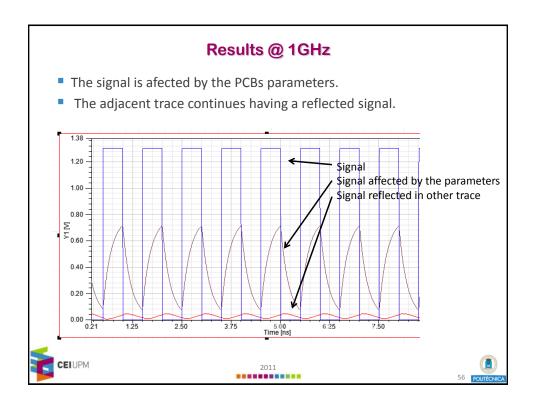

# Results @ 100 MHz • The signal has a small delay and a voltage drop. • The adjacent trace has a reflected signal. Signal 1.20 Signal affected by the parameters Signal reflected in other trace 1.00 0.80 ∑<sub>0.60</sub> 0.40 0.20 0.00 0.85 5.00 10.00 15.00 25.00 30.00 20.00 Time | 13 CEIUPM 2011

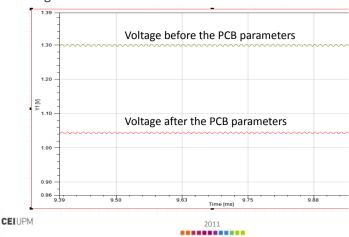

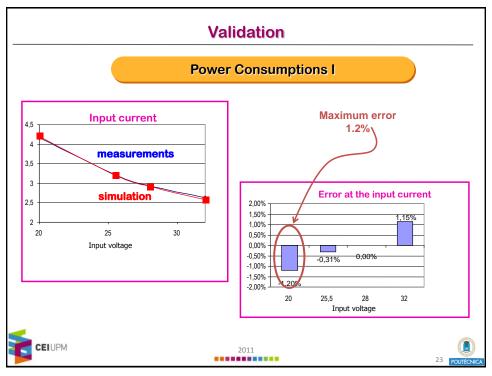

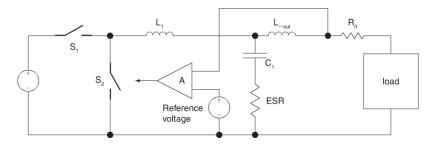

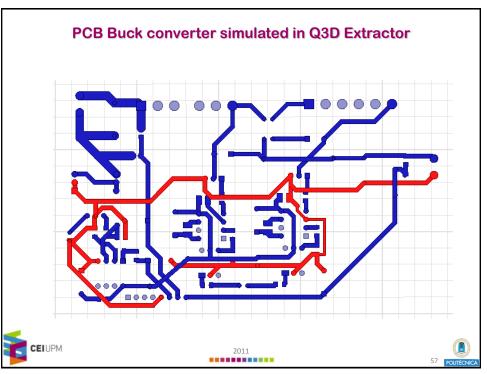

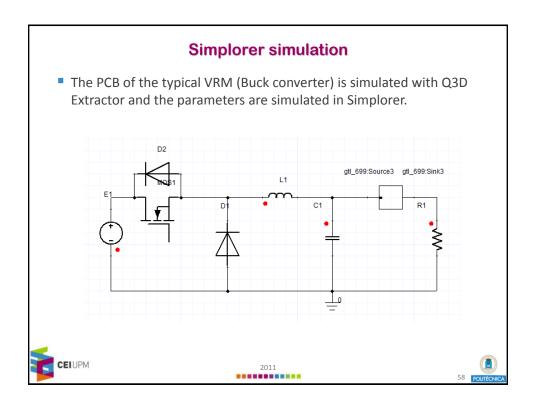

# **Results**

- The graph shows the output voltage of the VRM before and after the PCB parameters.

- It can be noticed that the voltage after the PCB parameters the voltage is lower.